# COFFEE Core USER MANUAL

# July 2007

#### **Contents**

- 1. Interface specification of the COFFEE RISC Core

- 1.1. Shared Data Bus

- 1.2. Interfacing coprocessors

- 2. Registers

- 2.1. General

- 2.2. Set 1: General Purpose Registers

- 2.3. Set 2: General Purpose Registers

- 2.4. Set 2: Special Purpose Registers

- 2.5. Condition Registers

- 2.6. CCB Registers

- 2.7. Register usage of a privileged user

- 2.8. Register limitations in 16 bit mode

- 2.9. Register value after reset

- 3. Timers

- 3.1. Timer registers

- 4. Processor Operating Mode

- 4.1. 16-bit and 32-bit decoding modes

- 4.2. Limitations in 16-bit mode

- 4.3. Super user mode

- 4.4. Resetting the processor

- 4.5. Configuring the processor

- 5. Interrupt and Exceptions

- 5.1. Interrupts

- 5.2. Exceptions

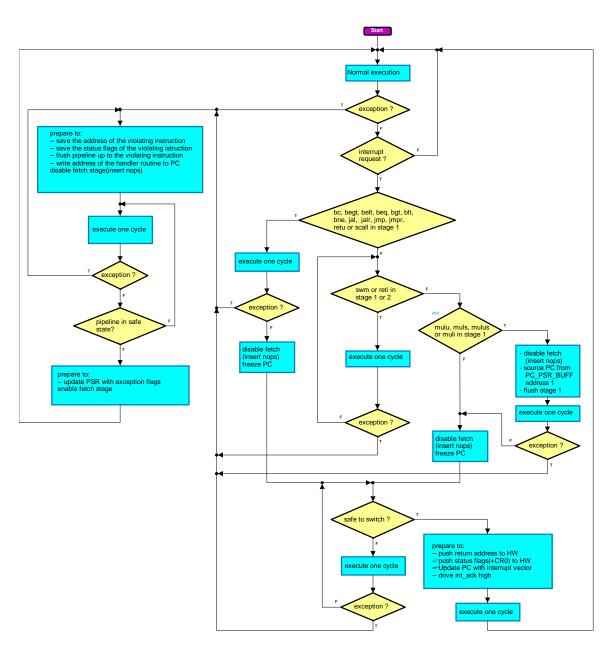

- 5.3. Handling interrupts and exceptions

# 6. Instruction Set Specifications

- 6.1. General information

- 6.2. Instruction definition

- 6.3. Instruction execution cycle times

- 6.4. ISA summary

# 1. Interface specification of the COFFEE RISC Core

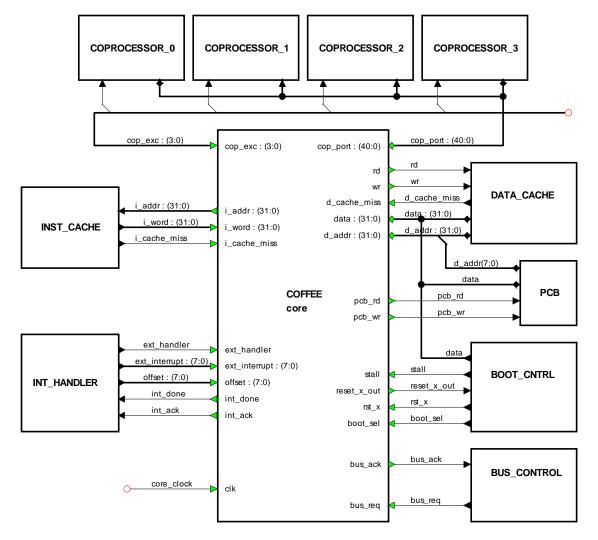

Figure 1.1 Core Interface

# 1.1. Shared data bus

COFFEE processor core allows sharing its data memory bus with other devices. In simple applications all peripherals and data memory can be connected directly to COFFEE core data bus. Multiprocessor systems with shared memory are also possible. However it should be noted that having too many devices communicating via shared bus eventually reduces performance since core will be stalled every time it needs the bus but it's not available.

#### Handshaking and accessing

Before accessing the bus, external device has to signal a request to COFFEE core. If multiple devices are connected, a bus arbiter must be used. Here, we assume that arbiter or some other device is communicating with core. Two signals are used for handshaking: *bus\_req* (input to core) and *bus\_ack* (output from core). Handshaking scheme is basically requesting and passing '*token*', that is the ownership of the bus.

An external device has to request the bus by asserting *bus\_req* signal. It can access the bus when core responds by asserting *bus\_ack* signal. This will happen immediately if core is not accessing the bus or after current access if the bus is reserved by core. An external device must hold *bus\_req* signal active throughout its access. It can perform several consecutive data transfers if core does not request the bus back (which is seen from *bus\_ack* -signal going low). When core requests the bus by driving *bus\_ack* -low an external device can finish current access, but must pass the token to core(this is only a recommendation, solution will depend on application). This is signaled by driving *bus\_req* low. If an external device has finished its access and has no further transfers, the token is automatically passed to core even if it does not request it. This happens when the device lowers *bus\_req* signal. This guarantees that the core can access the bus immediately if there's no traffic (in other words, core has the token by default). After reset, core owns the token.

This simple scheme should be adequate for most applications: it's fair since the bus cannot be locked by one device and it's predictable because the bus will be available as soon as an active access is finished. Also the core, which is assumed to use the bus mostly, does not have to request the token if there's no traffic on bus.

When an external device owns the token, core floats both address and data lines, read and write controls will be low (signals *rd*, *wr*, *pcb\_rd* and *pcb\_wr*). Likewise any other device must float the bus when core owns the token. Note that when core has the token but is not using the bus (bus idle cycle), it holds values of the last access on data and address lines (power saving feature).

Note, that read and write signals from multiple devices must be connected via OR gate because they are not tri-state signals. For detailed description of data memory interface signals, see COFFEE interface.

#### About timing

*Bus\_req* is an asynchronous input while *bus\_ack* is a synchronous output. Appropriate timing constraints must be applied to *bus\_req* to get correct results from synthesis if core is synthesized separately.

# Timing diagrams

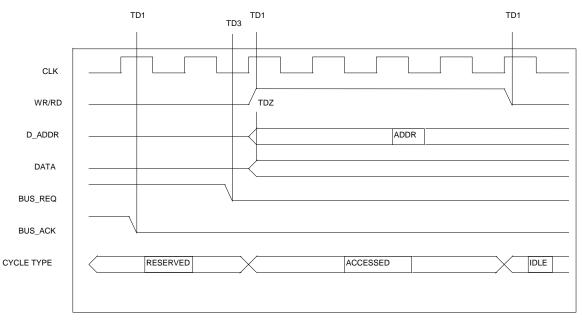

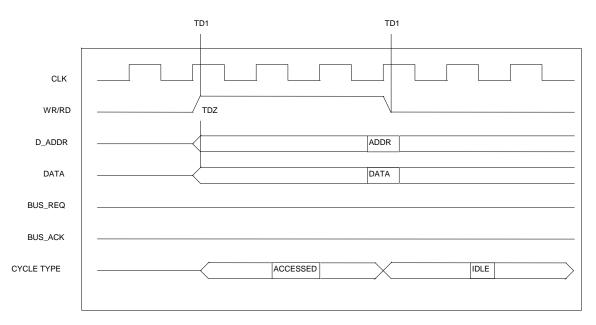

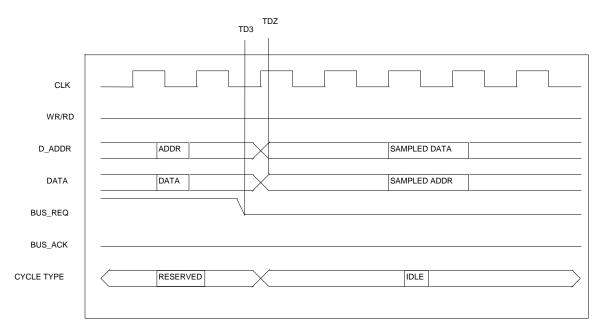

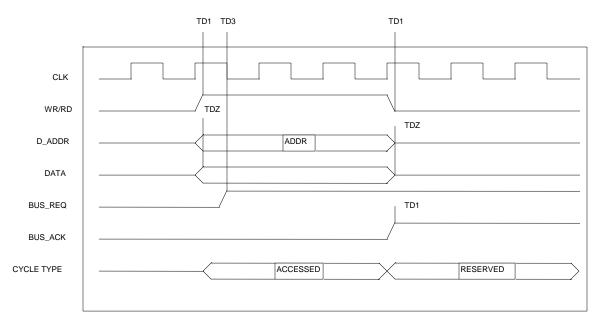

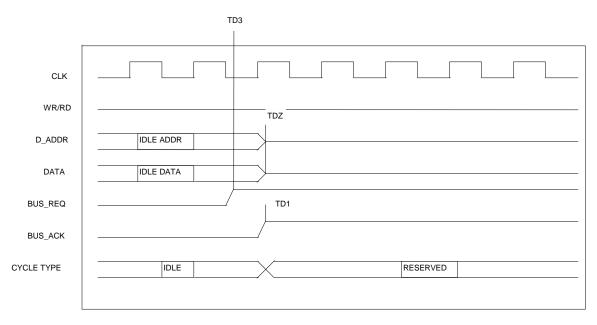

Figures T.5 through T.9 illustrate the timing of signals of the shared bus interface. Table 1 explains mnemonics and keywords. All delays are relative to previous rising edge of the clock CLK.

FIGURE T.5, DATA BUS STATE TRANSITION: RESERVED => ACCESSED

FIGURE T.6, DATA BUS STATE TRANSITION: RESERVED => IDLE

FIGURE T.8, DATA BUS STATE TRANSITION: ACCESSED => RESERVED

FIGURE T.9, DATA BUS STATE TRANSITION: IDLE => RESERVED

| Keyword   | Explanation                                        | Notes                      |

|-----------|----------------------------------------------------|----------------------------|

| TD1       | Delay from rising clock edge to the moment         | Technology                 |

|           | when data is valid on output of a D flip-flop.     | dependent.                 |

| TD3       | Maximum delay of the <i>bus_req</i> –signal. Refer | Suitable synthesis         |

|           | to results of preliminary synthesis.               | constraints for            |

|           |                                                    | <i>bus_req</i> –input must |

|           |                                                    | be set. See interface      |

|           |                                                    | specification.             |

| TDZ       | TD1 + delay of a tri-state gate                    | See synthesis notes        |

|           |                                                    | about handling tri-        |

|           |                                                    | state control signals.     |

| IDLE DATA | Data and address which are driven to bus by        |                            |

| IDLE ADDR | core when bus is in idle state. Should be the      |                            |

| SAMPLED   | values from previous access unless the bus is      |                            |

| DATA      | floated during the last RESERVED –cycle.           |                            |

| SAMPLED   |                                                    |                            |

| ADDR      |                                                    |                            |

| ADDR      | Valid address or data of an active access.         |                            |

| DATA      |                                                    |                            |

| IDLE      | Idle cycle of the bus, no active accesses. Core    |                            |

|           | drives last values on bus.                         |                            |

| ACCESSED  | Core owns the bus and is performing write or       |                            |

|           | read access.                                       |                            |

| RESERVED  | An external device owns the bus.                   |                            |

Table 1.1 Mnemonics and keywords used in figures T.5 through T.9

# **1.2.** Interfacing coprocessors

| g signals.<br><b>Direction</b> | Purpose/description                                                  |

|--------------------------------|----------------------------------------------------------------------|

| from the                       | when active                                                          |

| core side                      |                                                                      |

| In                             | Coprocessor exception.                                               |

|                                | Coprocessor can interrupt the                                        |

|                                | core by activating this signal.                                      |

|                                |                                                                      |

|                                |                                                                      |

| out                            | Write to cop. Write access to                                        |

|                                | coprocessor register file.                                           |

|                                |                                                                      |

| out                            | Read from cop. Read access to                                        |

|                                | coprocessor register file.                                           |

| out                            | Coprocessor index used to                                            |

|                                | address one of the four possible                                     |

|                                | coprocessors                                                         |

|                                |                                                                      |

| out                            | Register index used to select the                                    |

|                                | right register from the accessed                                     |

|                                | coprocessor register bank.                                           |

| inout                          | Data to/from the coprocessor.                                        |

|                                |                                                                      |

| in                             | Freezes the whole core! This                                         |

|                                | signal does not strictly speaking                                    |

|                                | belong to coprocessor interface                                      |

|                                | but can be used if no other                                          |

|                                | solution is available.                                               |

|                                | Direction<br>from the<br>core side<br>In<br>out<br>out<br>out<br>out |

Table 1.2 Coprocessor interfacing signals.

# 2. Registers

# 2.1. General

COFFEE has two different register sets. The first set (SET 1) is intended to be used by application programs. The second set of registers (SET 2) is for privileged software which could be an operating system or similar. SET 2 is protected from application program. Privileged software can access both sets. There's a total of 32 registers in both sets including general purpose registers (GPRs) and special purpose registers (SPRs).

In addition COFFEE has eight condition registers (CRs) which are used with conditional branches or when executing instructions conditionally. These are visible to application software as well as to privileged software.

Besides the register bank described here, COFFEE has another register bank, CCB (core control block), which is mapped to memory (accessed using load and store instructions). CCB is for controlling the processor operation and as such should be configured by boot code. CCB also contains few status registers. Note that, CCB can be extended with an external configuration block!

| Table 2.1 Registers |        |         |       |        |         |

|---------------------|--------|---------|-------|--------|---------|

| SET 1               |        |         | SET 2 |        |         |

| R0                  | GPR    | 32 bits | PR0   | GPR    | 32 bits |

| R1                  | GPR    | 32 bits | PR1   | GPR    | 32 bits |

|                     |        |         |       |        |         |

| R28                 | GPR    | 32 bits | PR28  | GPR    | 32 bits |

| R29                 | GPR    | 32 bits | PR29  | PSR    | 8 bits  |

| R30                 | GPR    | 32 bits | PR30  | SPSR   | 32 bits |

| R31                 | GPR/LR | 32 bits | PR31  | GPR/LR | 32 bits |

The usage of general purpose registers is not restricted by hardware in any way.

## 2.2. SET 1: General Purpose Registers

SET 1 has 32 identical general purpose registers R0...R31 with one exception: R31 is used as a link register (LR) with some instructions. The programmer is free to use R31 for any other purpose as long as its special behavior is taken into account. All general purpose registers (and the link register) are 32 bits wide.

#### 2.3. SET 2: General Purpose Registers

SET 2 has 30 identical general purpose registers PR0...PR28 and PR31 with one exception: PR31 is used as a link register by some instructions. The programmer is free to use PR31 for any other purpose as long as its special behavior is taken into account. All general purpose registers (and the link register) are 32 bits wide.

## 2.4. SET 2: Special Purpose Registers

There's two special purpose registers in SET 2: PSR and SPSR. PSR is eight bits wide. When reading data from PSR the 'non existent' bits are read as zeros. Writing to a read only register (PSR) is ignored.

#### PSR (register index 29)

Processor Status Register is a read only register and contains the flags explained below. Bits 7 .. 5 are reserved for future extensions.

| RESERVED | IE | IL | RSWR | RSRD | UM |

|----------|----|----|------|------|----|

| 75       | 4  | 3  | 2    | 1    | 0  |

- IE = 1: Interrupts enabled, IE = 0: Interrupts disabled.

- IL = 1: Instruction word length is 32 bits, IL = 0: Instruction word length is 16 bits.

- RSWR bit selects which register set to use as target:

- RSWR = 1: SET2, super users set; RSWR = 0: SET1, users set.

- RSRD bit selects which register set to use as source:

- RSRD = 1: SET2, super users set; RSRD = 0: SET1, users set.

- UM indicates which user mode the processor is in:

- UM = 0: super user mode, UM = 1: user mode.

• RESERVED: Read as zeros.

#### SPSR (register index 30)

SPRS is used to save PSR flags when changing user mode by executing *scall* instruction. It can be also used to set mode flags for the user: IE and IL flags are copied from SPSR to PSR when *retu* instruction is executed. Note that bits 31 .. 5 are writable but only bits 7 .. 0 are saved in case of *scall*.

## 2.5. Condition Registers

There are eight three bit wide condition registers C0...C7 (visible both to application software and privileged software). Condition registers are used with conditional branches or when executing instructions conditionally. Each register contains three flags: Z (Zero), N (Negative) and C (Carry). When executing compare instructions or some arithmetic instructions these three flags are calculated and saved to the selected CR (arithmetic instructions always save flags to C0). When conditionally branching or executing, flags from the selected CR are compared to match a certain condition given by the programmer. See chapters 'conditional execution' and 'instruction specifications' for more information.

# 2.6. CCB registers

Note, that 'byte' addresses (that is consecutive addresses) are used in table below. 256 consecutive addresses are reserved for core configuration block. Addresses beyond CCB\_BASE + FFh can be configured to point to an external peripheral configuration block (PCB), if present.

Registers which are shorter than 32 bits:

- LSB of a GPR corresponds to LSB of the short register in CCB.

- Unused bits read as zeros.

- For code compatibility with future versions, you should write unused bits as you would if there were more bits (interrupt masking, for example).

| Offset | ontrol block (CCB)<br>Mnemonic | Width | Description/usage                           | Notes                   |

|--------|--------------------------------|-------|---------------------------------------------|-------------------------|

| 00h    | CCB_BASE                       | 32    | The content of this register defines        | The base address has    |

|        | —                              |       | the base address of the CCB block.          | to be aligned to 256B   |

|        |                                |       | 256 consecutive memory locations            | boundary, that is, bits |

|        |                                |       | starting from [CCB_BASE] are                | 7 0 has to be zeros.    |

|        |                                |       | reserved for CCB registers. All             | You need to have at     |

|        |                                |       | memory accesses in range                    | least one instruction   |

|        |                                |       | [CCB_BASE] to [CCB_ ASE] +                  | between the one         |

|        |                                |       | 255 map to CCB registers.                   | remapping the CCB       |

|        |                                |       |                                             | (st instruction) and    |

|        |                                |       |                                             | one accessing CCB at    |

|        |                                |       |                                             | new location            |

| 01h    | PCB_BASE                       | 32    | The content of this register defines        | See note 2 below        |

|        |                                |       | the first address of peripheral address     |                         |

|        |                                |       | space. All memory accesses in range         |                         |

|        |                                |       | [PCB_BASE] to [PCB_END] map                 |                         |

|        |                                |       | to an external device(s) connected to       |                         |

|        |                                |       | data memory bus. Accesses to                |                         |

|        |                                |       | peripheral devices activate pcb_rd          |                         |

|        |                                |       | and <i>pcb_wr</i> signals instead of rd and |                         |

|        |                                |       | wr signals.                                 |                         |

| 02h    | PCB_END                        | 32    | The content of this register defines        |                         |

|        |                                |       | the last address of peripheral address      |                         |

|        |                                |       | space. All memory accesses in range         |                         |

|        |                                |       | [PCB_BASE] to [PCB_END] map to              |                         |

|        |                                |       | an external device(s) connected to          |                         |

|        |                                |       | data memory bus. Accesses to                |                         |

|        |                                |       | peripheral devices activate pcb_rd          |                         |

|        |                                |       | and <i>pcb_wr</i> signals instead of rd and |                         |

|        |                                |       | wr signals.                                 |                         |

| 03h    | PCB_AMASK                      | 32    | This register is used to define a mask      |                         |

|        |                                |       | for peripheral addresses. The address       |                         |

|        |                                |       | driven on address bus in constructed        |                         |

|        |                                |       | by masking the actual address with          |                         |

|        |                                |       | the contents of this register.              |                         |

| 04h    | COP0_INT_VEC                   | 32    | Co-processor 0 interrupt service            | See interrupts          |

|     |              |    | routine start address                                                                                                                                                                                                                                                                                                                                  |                                                                                               |

|-----|--------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| 05h | COP1_INT_VEC | 32 | Co-processor 1 interrupt service routine start address                                                                                                                                                                                                                                                                                                 | See interrupts                                                                                |

| 06h | COP2_INT_VEC | 32 | Co-processor 2 interrupt service routine start address                                                                                                                                                                                                                                                                                                 | See interrupts                                                                                |

| 07h | COP3_INT_VEC | 32 | Co-processor 3 interrupt service routine start address                                                                                                                                                                                                                                                                                                 | See interrupts                                                                                |

| 08h | EXT_INT0_VEC | 32 | External interrupt 0 service routine base address                                                                                                                                                                                                                                                                                                      | See interrupts                                                                                |

| 09h | EXT_INT1_VEC | 32 | External interrupt 1 service routine base address                                                                                                                                                                                                                                                                                                      | See interrupts                                                                                |

| Ah  | EXT_INT2_VEC | 32 | External interrupt 2 service routine base address                                                                                                                                                                                                                                                                                                      | See interrupts                                                                                |

| Bh  | EXT_INT3_VEC | 32 | External interrupt 3 service routine base address                                                                                                                                                                                                                                                                                                      | See interrupts                                                                                |

| Ch  | EXT_INT4_VEC | 32 | External interrupt 4 service routine base address                                                                                                                                                                                                                                                                                                      | See interrupts                                                                                |

| Dh  | EXT_INT5_VEC | 32 | External interrupt 5 service routine base address                                                                                                                                                                                                                                                                                                      | See interrupts                                                                                |

| Eh  | EXT_INT6_VEC | 32 | External interrupt 6 service routine base address                                                                                                                                                                                                                                                                                                      | See interrupts                                                                                |

| Fh  | EXT_INT7_VEC | 32 | External interrupt 7 service routine base address                                                                                                                                                                                                                                                                                                      | See interrupts                                                                                |

| 10h | INT_MODE_IL  | 12 | The content of this register defines<br>whether the interrupt service routines<br>should be executed in 16 bit mode or<br>in 32 bit mode. A high bit ('1')<br>causes the core to switch to 32 bit<br>mode when entering the interrupt<br>service routine in question, a low bit<br>('0') indicates execution of the<br>service routine in 16 bit mode. | Bit associations:<br>See note 3 below.<br>See interrupts and<br>processor status<br>register. |

| 111       INT_NODE_ONT       12       In contain to many spectra counties whether the interrupt service routines should be executed in user mode or in super-user mode. A high bit (11) causes the core to switch to user mode when entering the interrupt service routine in question, a low bit (0') indicates execution of the service routine in super-user mode.         12h       INT_MASK       12       Bits in this register can be used to block interrupt requests from the corresponding source to be blocked. A high bit (1') allows requests to pass through.         13h       INT_SERV       12       This is a read-only status register having a flag for each interrupt source. A high flag (1') means that an interrupt request from the corresponding source has been accepted. In practice this means that the interrupt service routine is being executed or it was executed until another request with higher priority interrupted the service routine. In this case there are multiple flags high in the INT_SERV register. Executing reti instruction at the end of an interrupt service routine will cause the corresponding flag to go low.                                                                                  | 11h  | INT_MODE_UM | 12 | The content of this register defines  |                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------|----|---------------------------------------|----------------|

| 12h       INT_MASK       12       Bits in this register can be used to block interrupt service routine in guestion, a low bit ('0') indicates execution of the service routine in super-user mode.         12h       INT_MASK       12       Bits in this register can be used to block interrupt requests from the corresponding source to be blocked. A high bit ('1') allows requests to pass through.         13h       INT_SERV       12       This is a read-only status register having a flag for cach interrupt source. A high flag ('1') means that an interrupt request from the corresponding source has been accepted. In practice this means that the interrupt service routine is being executed or it was executed until another request with higher priority interrupted the service routine. In this case there are multiple flags high in the INT_SERV register. Executing reti instruction at the end of an interrupt service routine will cause                                                                                                                                                                                                                                                                                     |      |             | 14 | -                                     |                |

| in super-user mode. A high bit ('1')         causes the core to switch to user         mode when entering the interrupt         service routine in question, a low bit         ('0') indicates execution of the         service routine in super-user mode.         12h       INT_MASK         12       Bits in this register can be used to         block interrupts from individual         sources. A low bit ('0') causes         interrupt requests from the         corresponding source to be blocked.         A high bit ('1') allows requests to         pass through.         13h         INT_SERV         12         This is a read-only status register         having a flag for each interrupt         source. A high flag ('1') means that         an interrupt request from the         corresponding source has been         accepted. In practice this means that         the interrupt service routine is being         executed or it was executed until         another request with higher priority         interrupted the service routine. In this         case there are multiple flags high in         the INT_SERV register. Executing         reti instruction at the end of an         interrupt service routine will cause |      |             |    |                                       |                |

| 12h       INT_MASK       12       Bits in this register can be used to block interrupt service routine in super-user mode.         12h       INT_MASK       12       Bits in this register can be used to block interrupt sfrom individual sources. A low bit ('0') causes interrupt requests from the corresponding source to be blocked. A high bit ('1') allows requests to pass through.       Read only. See interrupt source. A high flag ('1') means that an interrupt request from the corresponding source has been accepted. In practice this means that the interrupt service routine is being executed or it was executed until another request with higher priority interrupted the service routine. In this case there are multiple flags high in the INT_SERV register. Executing reti instruction at the end of an interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                  |      |             |    |                                       |                |

| Image: service routine in question, a low bit<br>('0') indicates execution of the<br>service routine in super-user mode.12hINT_MASK12Bits in this register can be used to<br>block interrupts from individual<br>sources. A low bit ('0') causes<br>interrupt requests from the<br>corresponding source to be blocked.<br>A high bit ('1') allows requests to<br>pass through.13hINT_SERV12This is a read-only status register<br>having a flag for each interrupt<br>source. A high flag ('1') means that<br>an interrupt request from the<br>corresponding source has been<br>accepted. In practice this means that<br>the interrupt service routine is being<br>executed or it was executed until<br>another request with higher priority<br>interrupted the service routine. In this<br>case there are multiple flags high in<br>the INT_SERV register. Executing<br><i>reti</i> instruction at the end of an<br>interrupt service routine will cause                                                                                                                                                                                                                                                                                                |      |             |    |                                       |                |

| service routine in question, a low bit       service routine in question, a low bit         ('0') indicates execution of the service routine in super-user mode.         12h       INT_MASK         12       Bits in this register can be used to block interrupts from individual sources. A low bit ('0') causes interrupt requests from the corresponding source to be blocked. A high bit ('1') allows requests to pass through.         13h       INT_SERV         12       This is a read-only status register having a flag for each interrupt source. A high flag ('1') means that an interrupt request from the corresponding source has been accepted. In practice this means that the interrupt service routine is being executed or it was executed until another request with higher priority interrupted the service routine. In this case there are multiple flags high in the INT_SERV register. Executing reti instruction at the end of an interrupt service routine will cause                                                                                                                                                                                                                                                        |      |             |    |                                       |                |

| (°0°) indicates execution of the service routine in super-user mode.         12h       INT_MASK       12       Bits in this register can be used to block interrupts from individual sources. A low bit (°0°) causes interrupt requests from the corresponding source to be blocked. A high bit (°1°) allows requests to pass through.         13h       INT_SERV       12       This is a read-only status register having a flag for each interrupt source. A high flag (°1°) means that an interrupt request from the corresponding source has been accepted. In practice this means that the interrupt service routine is being executed or it was executed until another request with higher priority interrupted the service routine. In this case there are multiple flags high in the INT_SERV register. Executing reti instruction at the end of an interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                        |      |             |    |                                       |                |

| 12h       INT_MASK       12       Bits in this register can be used to block interrupts from individual sources. A low bit ('0') causes interrupt requests from the corresponding source to be blocked. A high bit ('1') allows requests to pass through.         13h       INT_SERV       12       This is a read-only status register having a flag for each interrupt source. A high flag ('1') means that an interrupt request from the corresponding source has been accepted. In practice this means that the interrupt service routine is being executed or it was executed until another request with higher priority interrupted the service routine. In this case there are multiple flags high in the INT_SERV register. Executing reti instruction at the end of an interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |             |    | -                                     |                |

| 12h       INT_MASK       12       Bits in this register can be used to block interrupts from individual sources. A low bit ('0') causes interrupt requests from the corresponding source to be blocked. A high bit ('1') allows requests to pass through.         13h       INT_SERV       12       This is a read-only status register having a flag for each interrupt source. A high flag ('1') means that an interrupt request from the corresponding source has been accepted. In practice this means that the interrupt service routine is being executed or it was executed until another request with higher priority interrupted the service routine. In this case there are multiple flags high in the INT_SERV register. Executing reti instruction at the end of an interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |             |    |                                       |                |

| block interrupts from individual sources. A low bit ('0') causes interrupt requests from the corresponding source to be blocked. A high bit ('1') allows requests to pass through.       Read only. See having a flag for each interrupt interrupts.         13h       INT_SERV       12       This is a read-only status register having a flag for each interrupt source. A high flag ('1') means that an interrupt request from the corresponding source has been accepted. In practice this means that the interrupt service routine is being executed or it was executed until another request with higher priority interrupted the service routine. In this case there are multiple flags high in the INT_SERV register. Executing reti instruction at the end of an interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12h  | INT MASK    | 12 | -                                     |                |

| 13h       INT_SERV       12       This is a read-only status register having a flag for each interrupt source. A high flag ('1') means that an interrupt request from the corresponding source has been accepted. In practice this means that the interrupt service routine is being executed or it was executed until another request with higher priority interrupted the service routine. In this case there are multiple flags high in the INT_SERV register. Executing reti instruction at the end of an interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1211 |             | 12 | -                                     |                |

| Image: constraint of the constraint of the corresponding source to be blocked.<br>A high bit ('1') allows requests to pass through.Read only.13hINT_SERV12This is a read-only status register having a flag for each interrupt source. A high flag ('1') means that an interrupt request from the corresponding source has been accepted. In practice this means that the interrupt service routine is being executed or it was executed until another request with higher priority interrupted the service routine. In this case there are multiple flags high in the INT_SERV register. Executing reti instruction at the end of an interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |             |    | -                                     |                |

| 13h       INT_SERV       12       This is a read-only status register having a flag for each interrupt interrupts.         13h       INT_SERV       12       This is a read-only status register having a flag for each interrupt interrupts.         source. A high flag ('1') means that an interrupt request from the corresponding source has been accepted. In practice this means that the interrupt service routine is being executed or it was executed until another request with higher priority interrupted the service routine. In this case there are multiple flags high in the INT_SERV register. Executing <i>reti</i> instruction at the end of an interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |             |    |                                       |                |

| A high bit ('1') allows requests to<br>pass through.Read only. See<br>interrupt13hINT_SERV12This is a read-only status register<br>having a flag for each interrupt<br>source. A high flag ('1') means that<br>an interrupt request from the<br>corresponding source has been<br>accepted. In practice this means that<br>the interrupt service routine is being<br>executed or it was executed until<br>another request with higher priority<br>interrupted the service routine. In this<br>case there are multiple flags high in<br>the INT_SERV register. Executing<br><i>reti</i> instruction at the end of an<br>interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |             |    | 1 1                                   |                |

| 13h       INT_SERV       12       This is a read-only status register having a flag for each interrupt source. A high flag ('1') means that an interrupt request from the corresponding source has been accepted. In practice this means that the interrupt service routine is being executed or it was executed until another request with higher priority interrupted the service routine. In this case there are multiple flags high in the INT_SERV register. Executing reti instruction at the end of an interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |             |    |                                       |                |

| 13h       INT_SERV       12       This is a read-only status register having a flag for each interrupt interrupts.       Read only. See interrupt source. A high flag ('1') means that an interrupt request from the corresponding source has been accepted. In practice this means that the interrupt service routine is being executed or it was executed until another request with higher priority interrupted the service routine. In this case there are multiple flags high in the INT_SERV register. Executing reti instruction at the end of an interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |             |    |                                       |                |

| having a flag for each interrupt interrupts.<br>source. A high flag ('1') means that<br>an interrupt request from the<br>corresponding source has been<br>accepted. In practice this means that<br>the interrupt service routine is being<br>executed or it was executed until<br>another request with higher priority<br>interrupted the service routine. In this<br>case there are multiple flags high in<br>the INT_SERV register. Executing<br><i>reti</i> instruction at the end of an<br>interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13h  | INT SERV    | 12 |                                       | Read only. See |

| source. A high flag ('1') means that<br>an interrupt request from the<br>corresponding source has been<br>accepted. In practice this means that<br>the interrupt service routine is being<br>executed or it was executed until<br>another request with higher priority<br>interrupted the service routine. In this<br>case there are multiple flags high in<br>the INT_SERV register. Executing<br><i>reti</i> instruction at the end of an<br>interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |             |    |                                       | interrupts.    |

| an interrupt request from the<br>corresponding source has been<br>accepted. In practice this means that<br>the interrupt service routine is being<br>executed or it was executed until<br>another request with higher priority<br>interrupted the service routine. In this<br>case there are multiple flags high in<br>the INT_SERV register. Executing<br><i>reti</i> instruction at the end of an<br>interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |             |    |                                       | •              |

| corresponding source has been<br>accepted. In practice this means that<br>the interrupt service routine is being<br>executed or it was executed until<br>another request with higher priority<br>interrupted the service routine. In this<br>case there are multiple flags high in<br>the INT_SERV register. Executing<br><i>reti</i> instruction at the end of an<br>interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |             |    |                                       |                |

| accepted. In practice this means that<br>the interrupt service routine is being<br>executed or it was executed until<br>another request with higher priority<br>interrupted the service routine. In this<br>case there are multiple flags high in<br>the INT_SERV register. Executing<br><i>reti</i> instruction at the end of an<br>interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |             |    |                                       |                |

| the interrupt service routine is being<br>executed or it was executed until<br>another request with higher priority<br>interrupted the service routine. In this<br>case there are multiple flags high in<br>the INT_SERV register. Executing<br><i>reti</i> instruction at the end of an<br>interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |             |    |                                       |                |

| another request with higher priority<br>interrupted the service routine. In this<br>case there are multiple flags high in<br>the INT_SERV register. Executing<br><i>reti</i> instruction at the end of an<br>interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |             |    |                                       |                |

| interrupted the service routine. In this<br>case there are multiple flags high in<br>the INT_SERV register. Executing<br><i>reti</i> instruction at the end of an<br>interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |             |    |                                       |                |

| interrupted the service routine. In this<br>case there are multiple flags high in<br>the INT_SERV register. Executing<br><i>reti</i> instruction at the end of an<br>interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |             |    | another request with higher priority  |                |

| the INT_SERV register. Executing<br><i>reti</i> instruction at the end of an<br>interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |             |    |                                       |                |

| the INT_SERV register. Executing<br><i>reti</i> instruction at the end of an<br>interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |             |    | case there are multiple flags high in |                |

| <i>reti</i> instruction at the end of an interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |             |    |                                       |                |

| interrupt service routine will cause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |             |    |                                       |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |             |    | interrupt service routine will cause  |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |             |    | -                                     |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |             |    |                                       |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |             |    |                                       |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |             |    |                                       |                |

| 14h  | INT_PEND    | 12 | This is a read-only status register      |                         |

|------|-------------|----|------------------------------------------|-------------------------|

| 1411 | IINI_PEND   | 12 | having a flag for each interrupt         |                         |

|      |             |    |                                          |                         |

|      |             |    | source. A high flag ('1') means that     |                         |

|      |             |    | an interrupt request from the            |                         |

|      |             |    | corresponding source has been            |                         |

|      |             |    | detected and is waiting to get           |                         |

|      |             |    | accepted. A flag is lowered once the     |                         |

|      |             |    | request is accepted and the service      |                         |

|      |             |    | routine started.                         |                         |

| 15h  | EXT_INT_PRI | 32 | This register is used to set priorities  | 0 – highest priority    |

|      |             |    | for external interrupt sources. Each     | 15– lowest priority     |

|      |             |    | interrupt source is associated with a    | Priorities for external |

|      |             |    | four bit unsigned value in range from    | interrupts can only be  |

|      |             |    | 0 to 15, 0 meaning highest priority.     | set if external handler |

|      |             |    | Bit field <b>PRIX</b> is associated with | is not used.            |

|      |             |    | external interrupt number X. X varies    |                         |

|      |             |    | from 0 to 7.                             |                         |

|      |             |    | Interrupt priorities:                    |                         |

|      |             |    | Bits 31 28 : INT 7 priority              |                         |

|      |             |    | Bits 27 24 : INT 6 priority              |                         |

|      |             |    |                                          |                         |

|      |             |    | Bits 7 4 : INT 1 priority                |                         |

|      |             |    | Bits 3 0 : INT 0 priority                |                         |

| 16h  | COP_INT_PRI | 16 | This register is used to set priorities  |                         |

|      |             |    | for coprocessor interrupts/exceptions.   |                         |

|      |             |    | Each coprocessor is associated with a    |                         |

|      |             |    | four bit unsigned value in range from    |                         |

|      |             |    | 0 to 15, 0 meaning highest priority.     |                         |

|      |             |    | Bit field <b>PRIX</b> is associated with |                         |

|      |             |    | coprocessor number X. X varies from      |                         |

|      |             |    | 0 to 3.                                  |                         |

|      |             |    | Bits 15 12 : COP3 priority               |                         |

|      |             |    | Bits 11 8 : COP2 priority                |                         |

|      |             |    | Bits 7 4 : COP1 priority                 |                         |

|      |             |    | Bits 30 : COP0 priority                  |                         |

|      |             |    |                                          |                         |

| 17h | EXCEPTION_CS  | 8  | This is a read-only register which is  | Read only. See     |

|-----|---------------|----|----------------------------------------|--------------------|

|     | _             |    | used to report the cause of an         | exceptions.        |

|     |               |    | exception to an exception handler.     |                    |

| 18h | EXCEPTION_PC  | 32 | This is a read-only register which is  |                    |

|     | _             |    | used to report the memory address of   |                    |

|     |               |    | the instruction which caused an        |                    |

|     |               |    | exception. It can be used by           |                    |

|     |               |    | exception handler.                     |                    |

| 19h | EXCEPTION_PSR | 8  | Contains a copy of processor status    |                    |

|     | _             |    | flags (PSR) which were valid when      |                    |

|     |               |    | the instruction causing an exception   |                    |

|     |               |    | was decoded. It can be used by         |                    |

|     |               |    | exception handler.                     |                    |

| 1Ah | DMEM_BOUND_LO | 32 | This register is used to set the lower | The CCB block can  |

|     |               |    | limit of a continuous address space    | be protected from  |

|     |               |    | for data memory protection.            | user level code by |

|     |               |    | Accesses inside the area defined       | mapping it to      |

|     |               |    | together with DMEM_BOUND_HI            | protected address  |

|     |               |    | register are either allowed in user    | space. See         |

|     |               |    | mode or blocked while in user mode     | programming        |

|     |               |    | (allowing accesses outside the area    | considerations.    |

|     |               |    | only) depending on memory              |                    |

|     |               |    | protection flags in MEM_CONF           |                    |

|     |               |    | register. In super user mode the       |                    |

|     |               |    | whole address space is accessible.     |                    |

| 1Bh | DMEM_BOUND_HI | 32 | This register is used to set the upper |                    |