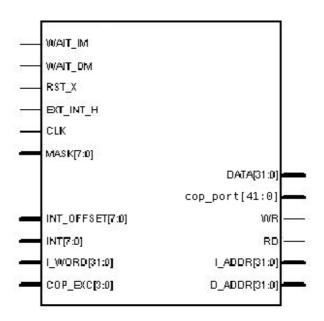

## **Interface of the Core**

## Ports of the interface

**WAIT\_IM**: Intruction cache singal to the core. Instruction cache signals to the core to wait in case of a miss.

**WAIT\_DM**: Data cache signal to the core. Data cache signals to the core to wait in case of a miss.

**RST\_X**: Reset signal, active low

**EXT\_INT\_H**: External interrupt handler signal. When high, core assumes that an external interrupt handler is present and uses **INT\_OFFSET** - signal when calculating handler routine address.

**CLK**: System clock

**MASK[7..0]**: Mask vector for external interrupts. Each signal corresponds to one interrupt source. If the signal is high, the exception is enabled, and if the signal is low, the exception is disabled.

**INT\_OFFSET[7..0]**: Interrupt address offset signal. This signal is used if and only if the **EXT\_INT\_H** - signal is high. With this signal, the interrupt address is calculated as follows:

reg\_addr(31 downto 12) & INT\_OFFSET[7 downto 0] & "0000"

The **reg\_addr**(31 downto 12) equals the upper 20 bits of the value in the corresponding interrupt register.

**INT[7..0]**: Signals from interrupt sources or from the external interrupt handler, if present. Each signal corresponds to one interrupt source. The signal is sensitive to a falling edge. The signal must be high at least 2 clock cycles before the falling edge.

**I\_WORD[31..0]**: Data from the instruction cache.

**COP\_EXC[3..0]**: Co- processor exception signal to the core. Each signal corresponds to one co- processor, and is active when high. The serving mechanism is the same as for interrupts, but the co- processor interrupts are not maskable.

**DATA[31..0]**: Data to/from the Data-cache.

**COP\_PORT[41..0]**: Co-processor bus. Signalling of the bus is declared as follows:

cop\_port(41) <= wait

cop\_port(40) <= wr\_cop

cop\_port(39) <= rd\_cop

cop\_port(38 downto 37) <= c\_index

cop\_port(36 downto 32) <= r\_index

cop\_port(31 downto 0) <= data</pre>

wr\_cop : write signal

rd\_cop : read signal

**c\_index**: number of the co-processor to work with (2 bits)

**r\_index** : number of the co-processor register to work with (5 bits)

data: Data to or from a coprocessor.

**WR**: Data cache write signal. Active when high.

**RD**: Data cache read signal. Active when high.

**I\_ADDR[31..0]**: Address of the requested item from the instruction cache.

**D\_ADDR[31..0]**: Address of the requested item from the data cache